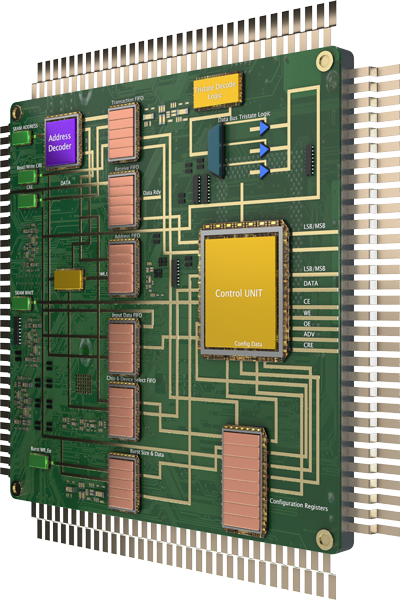

SRAM Controller

The Nand Logic SRAM controller can control up to 8 SRAM devices. Control of each device can be handled independently on a transaction-by-transaction basis. The controller provides support for Page Mode, Asynchronous Mode, and Burst Mode. Further, each slave can be configured for any mode, independent of all other slave devices.

Key Features

- Up to 8 Slave FLASH Ports

- Independent Port Configuration

- Independent Transaction Queuing

- Configuration Registers R/W

- Configurable Erase Operations

- Security Configuration

- Burst Mode Support

- Page Mode Support

- Asynchronous Mode Support

- Full Synthesizable

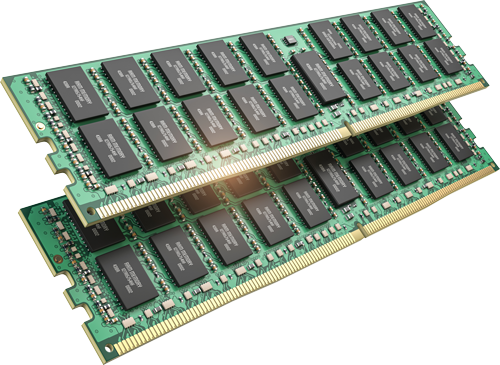

DDR Controller

The Nand Logic DDR controller supports industry standard DDR memory devices of size 8, 16, and 32 bits. The controller provides a number of features that allow for quick access to data stored in the individual banks and rows. Features such as automatic bank refreshing and row activation ensure that data is stored or retrieved as fast as possible upon request , thus increasing application efficiency and performance.

Key Features

- + 8 Slave DDR Ports

- 16/32-bit DDR SDRAM Data Interface

- Independent Slave Device Configuration

- Auto-Write Leveling Feature

- Programmable Burst Length

- Automatic Refresh

- Mode Register Programming

- Automatic Row Activation

- Fully Synthesizable

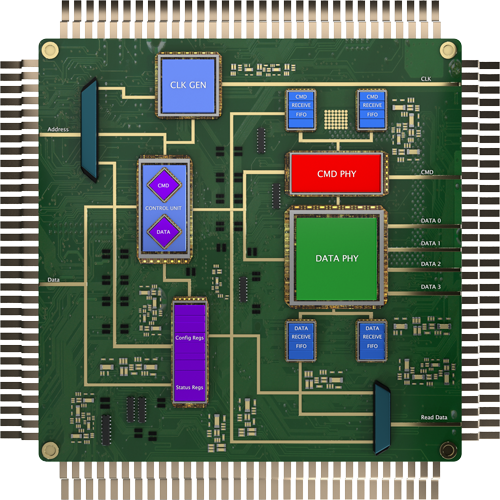

SDIO Interface

The SDIO Protocol is a widely used bus for interfacing peripheral devices to embedded processors. Operating at up to 200Mhz, the protocol was designed for high throughput applications. We maximize this throughput by providing a FIFO-like structure for both inbound and outbound data. Our interface controller and driver simplifies much of the protocol ins and outs and allows the embedded application developer to use the interface bus as a very simple physical layer transport mechanism, as it should be.

Therefore, over-complicated drivers attached to an OS are not necessary to take advantage of the bus. Our straight-forward method of transmitting data ensures that there are NO WASTED cycles or unnecessary software overhead.

Key Features

- Independent Command & Data Channels

- Automated SD Initiation Sequence

- Independent Transaction Queuing

- Configurable Function Table

- Automated Interrupt Handler